- 您现在的位置:买卖IC网 > Sheet目录1999 > ICS94201DFLF (IDT, Integrated Device Technology Inc)IC FREQ GENERATOR PROGR 56-SSOP

16

ICS94201

0428B - 11/28/05

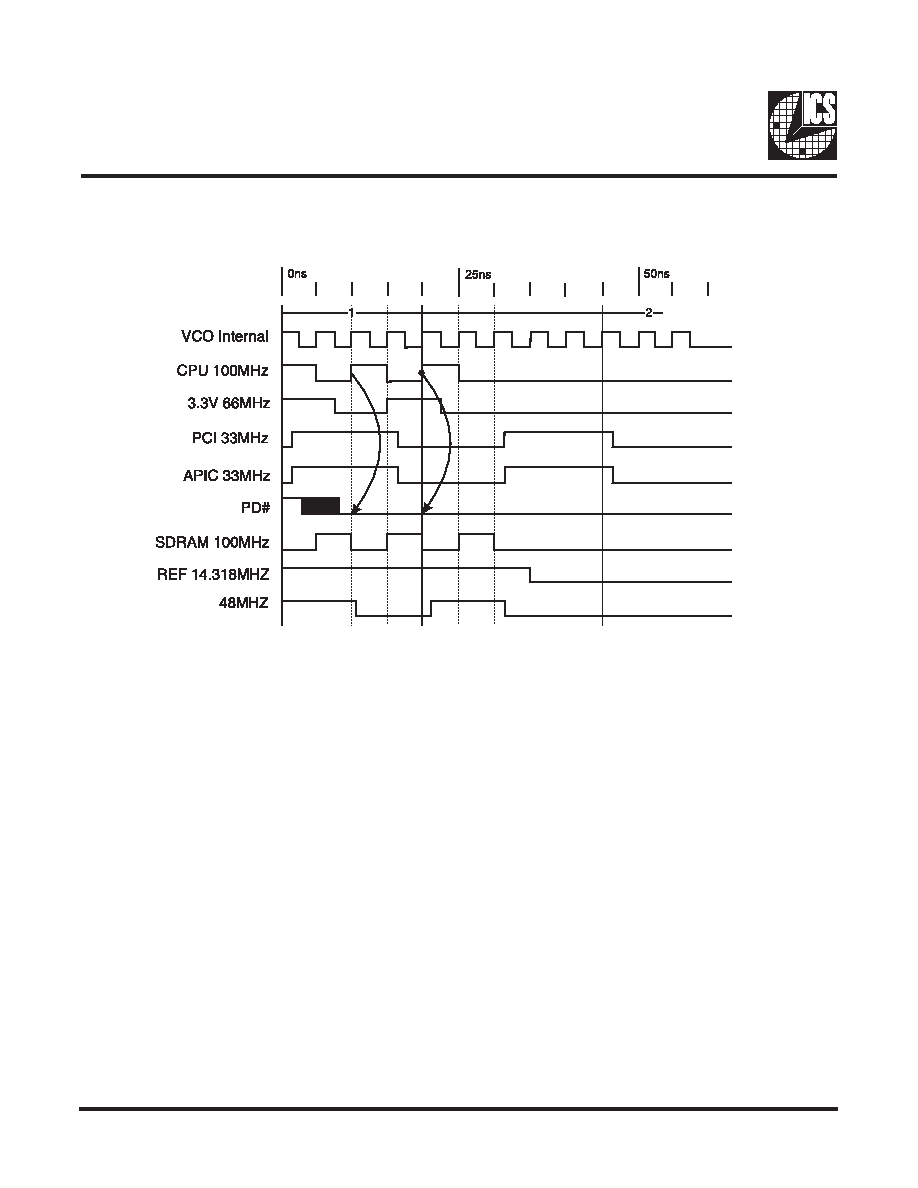

Power Down Waveform

Note

1. After PD# is sampled active (Low) for 2 consective rising edges of CPUCLKs, all the

output clocks are driven Low on their next High to Low tranistiion.

2. Power-up latency <3ms.

3. Waveform shown for 100MHz

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ICS950218AF

IC TIMING CTRL HUB P4 48-SSOP

ICS950908BFLF

IC TIMING CTRL HUB P4 56-SSOP

ICS951402AGLF

IC TIMING CTRL HUB P4 48-TSSOP

ICS95V847AGIT

IC CLOCK DRIVER 2.5V 24-TSSOP

ICS95V850AGT

IC CLK DVR PLL 1:10 48TSSOP

ICS95V857ALT

IC CLK DVR PLL 1:10 40TVSOP

ICS95V857CKLF8

IC CLK DVR PLL 1:10 40VFQFN

ICS97U870AKT

IC CLK DVR PLL 1:10 40VFQFN

相关代理商/技术参数

ICS94201DFLFT

功能描述:IC FREQ GENERATOR PROGR 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

ICS94201DFT

功能描述:IC FREQ GENERATOR PROGR 56-SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

ICS94201YFT

制造商:ICS 制造商全称:ICS 功能描述:Programmable System Frequency Generator for PII/III⑩

ICS94203

制造商:ICS 制造商全称:ICS 功能描述:Programmable System Frequency Generator for PII/III⑩

ICS94203F-T

制造商:ICS 制造商全称:ICS 功能描述:Peripheral IC

ICS94203YF-T

制造商:ICS 制造商全称:ICS 功能描述:Programmable System Frequency Generator for PII/III⑩

ICS94206

制造商:ICS 制造商全称:ICS 功能描述:Programmable System Frequency Generator for PII/III⑩

ICS94206YF-T

制造商:ICS 制造商全称:ICS 功能描述:Programmable System Frequency Generator for PII/III⑩